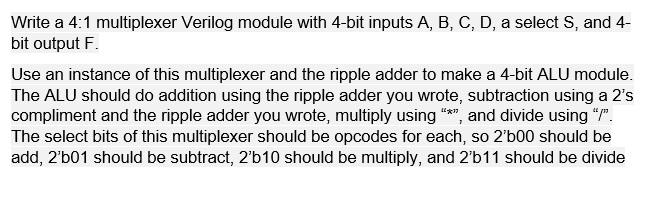

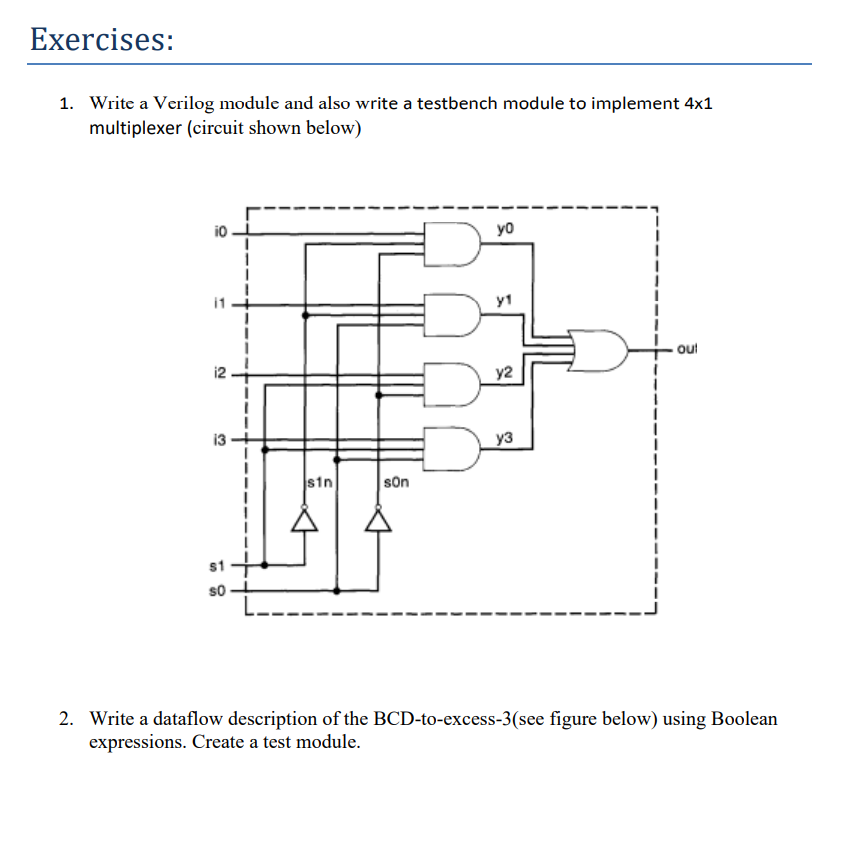

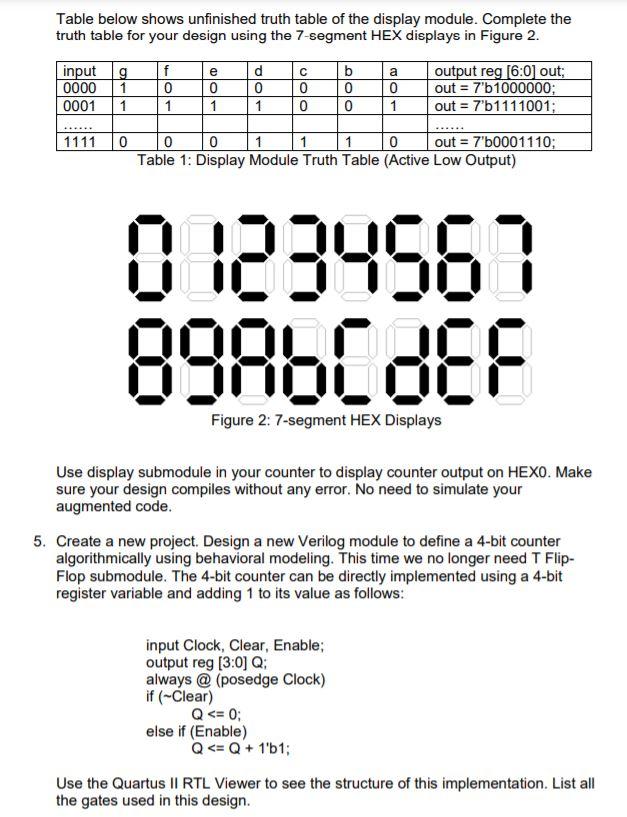

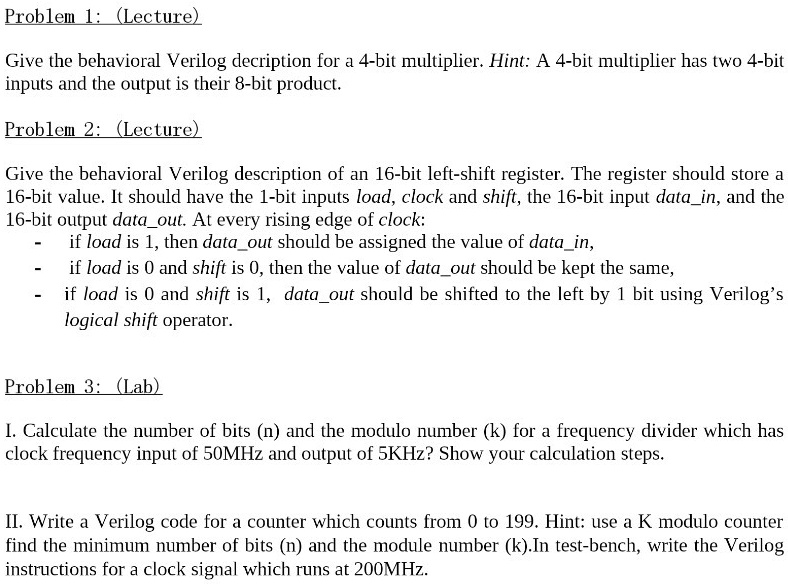

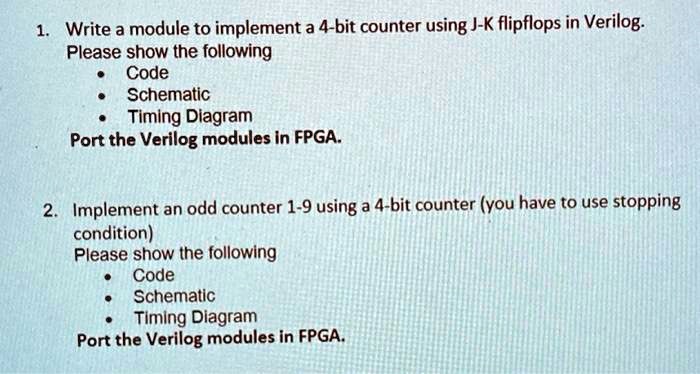

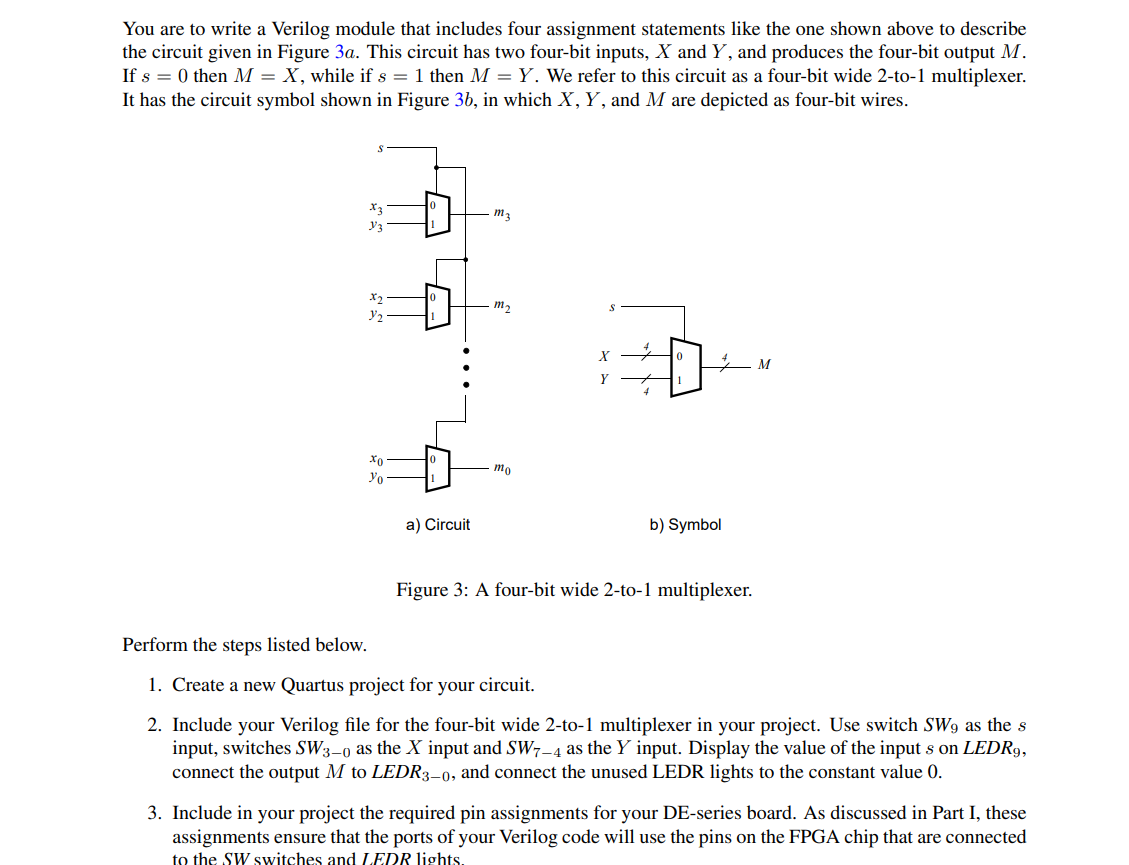

Celebrate heritage through substantial collections of culturally-rich solved write two verilog modules to design a 4-bits divisor photographs. honoring cultural traditions of artistic, creative, and painting. ideal for diversity and inclusion initiatives. Discover high-resolution solved write two verilog modules to design a 4-bits divisor images optimized for various applications. Suitable for various applications including web design, social media, personal projects, and digital content creation All solved write two verilog modules to design a 4-bits divisor images are available in high resolution with professional-grade quality, optimized for both digital and print applications, and include comprehensive metadata for easy organization and usage. Our solved write two verilog modules to design a 4-bits divisor gallery offers diverse visual resources to bring your ideas to life. Instant download capabilities enable immediate access to chosen solved write two verilog modules to design a 4-bits divisor images. Advanced search capabilities make finding the perfect solved write two verilog modules to design a 4-bits divisor image effortless and efficient. Reliable customer support ensures smooth experience throughout the solved write two verilog modules to design a 4-bits divisor selection process. Multiple resolution options ensure optimal performance across different platforms and applications. Professional licensing options accommodate both commercial and educational usage requirements.

![[Solved] Problem 2 Write a System Verilog module for an 2:1 Multiplexer ...](https://mavink.com/images/loadingwhitetransparent.gif)

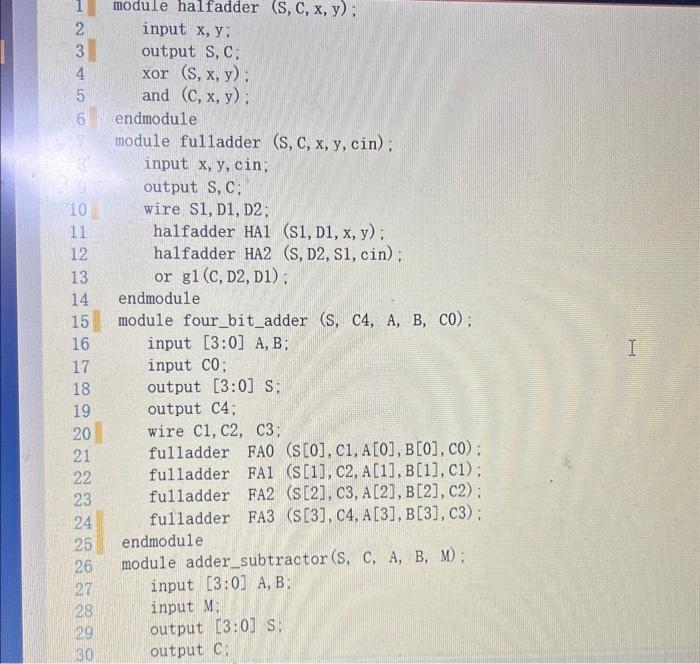

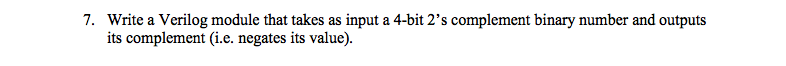

![Question No 2: (CLO-1) [10 Marks] Write a Verilog code to implement the ...](https://cdn.numerade.com/ask_images/79cb2d085d1348f9bb806b16a1c6f376.jpg)

![Solved by an EXPERT Problem pts] Write a Verilog code for a 4-bit ...](https://media.cheggcdn.com/study/9cd/9cd3d5f7-c8c3-4192-93c4-2e3f59d93539/image.jpg)

![[Solved] Write a Verilog module to describe the 4 | SolutionInn](https://s3.amazonaws.com/si.question.images/images/question_images/1662/2/0/4/93763133c09177da1662204888446.jpg)

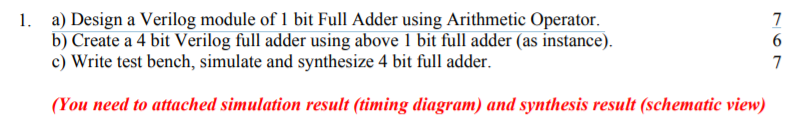

![[GET ANSWER] 5. a) Design a Verilog model of 1-bit full adder using ...](https://cdn.numerade.com/ask_images/7ba43eeb307148d6b4a0b1a46ebf42cb.jpg)

![[Solved]: Using Verilog language, design an 4bit ALU that ca](https://media.cheggcdn.com/media/d8c/d8c7a825-edcb-478f-9c2c-fc6206eb76fa/phpLlhQ8H)

![Solved 2. [4 Pts] Write a Verilog module for the circuit | Chegg.com](https://media.cheggcdn.com/media/c33/c33b0eff-03ac-4917-be54-e93072565a7b/php7GZSMO)